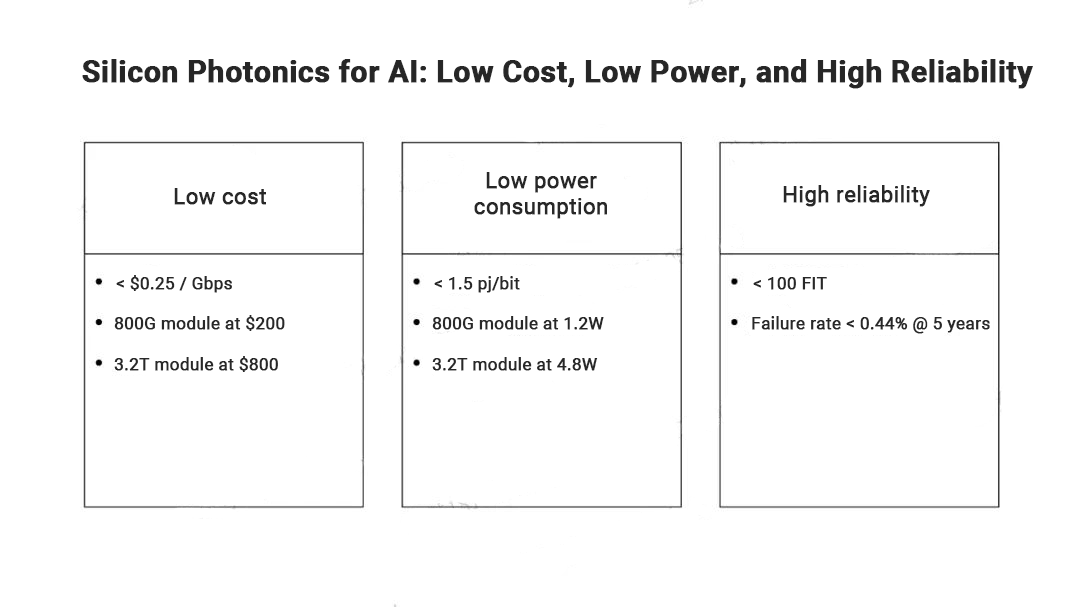

Silicon photonics technology in AI scenarios prioritizes three core demands: low cost, low power consumption, and high reliability, aligning with NVIDIA's requirements.

Three core requirements of silicon photonics technology in AI

Three core requirements of silicon photonics technology in AI

Low Cost

Aiming for a cost of $0.25 per Gbps, which is about a quarter of current optical module costs. The goal is to afford a high-capacity, highly integrated 3.2T silicon photonics module at the price of today's 800G module. Broadcom's 2023 release of a 6.4T CPO silicon photonics module shows promising advancements in reducing costs as the industry matures.

Low Power Consumption

Achieving low power consumption remains a significant technical challenge.

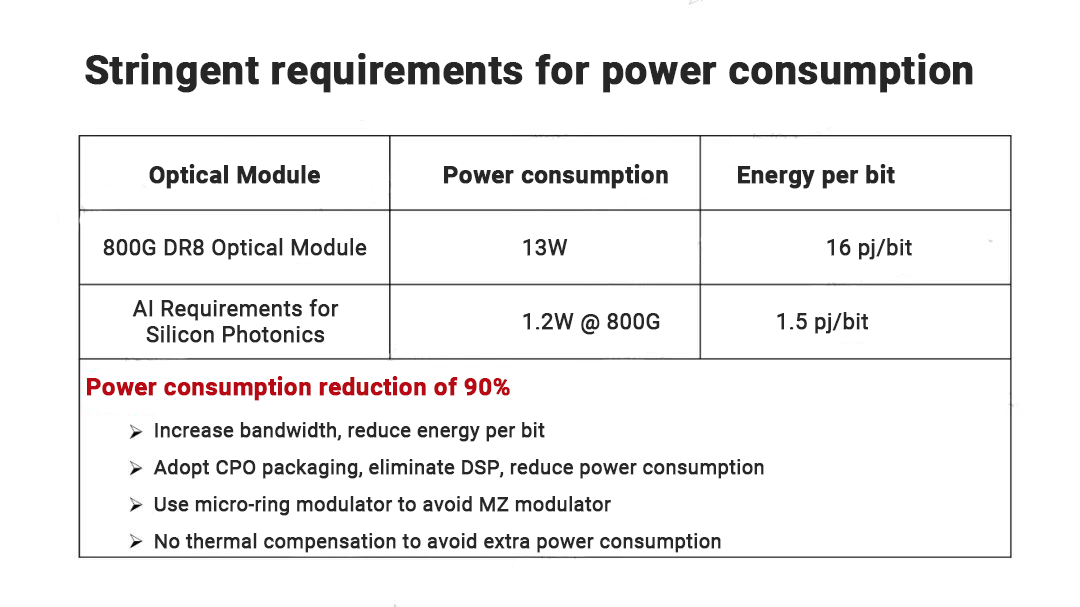

Stringent requirement for power consumption

Stringent requirement for power consumption

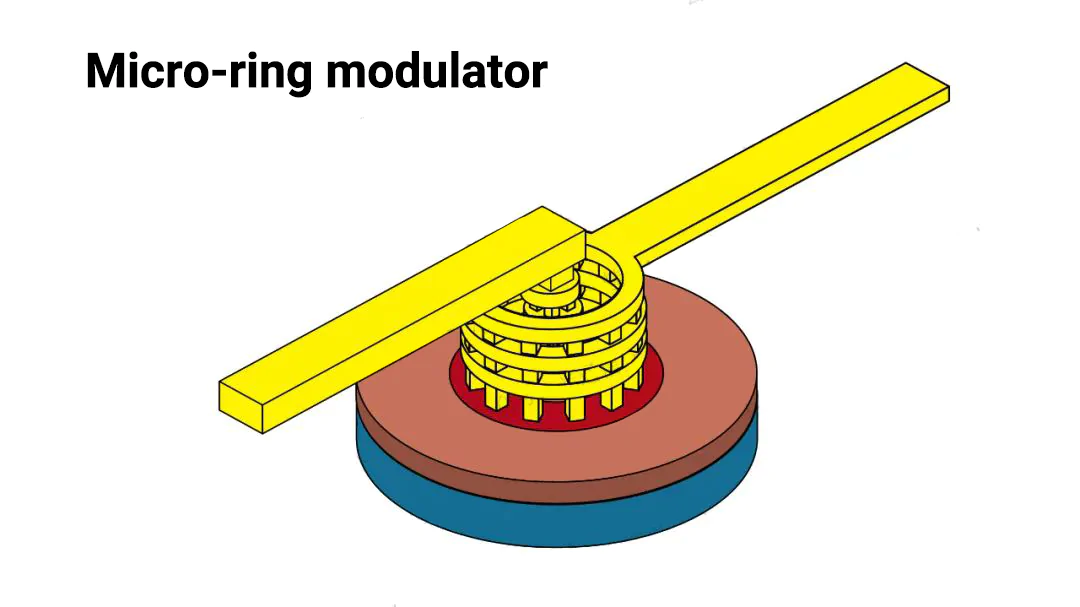

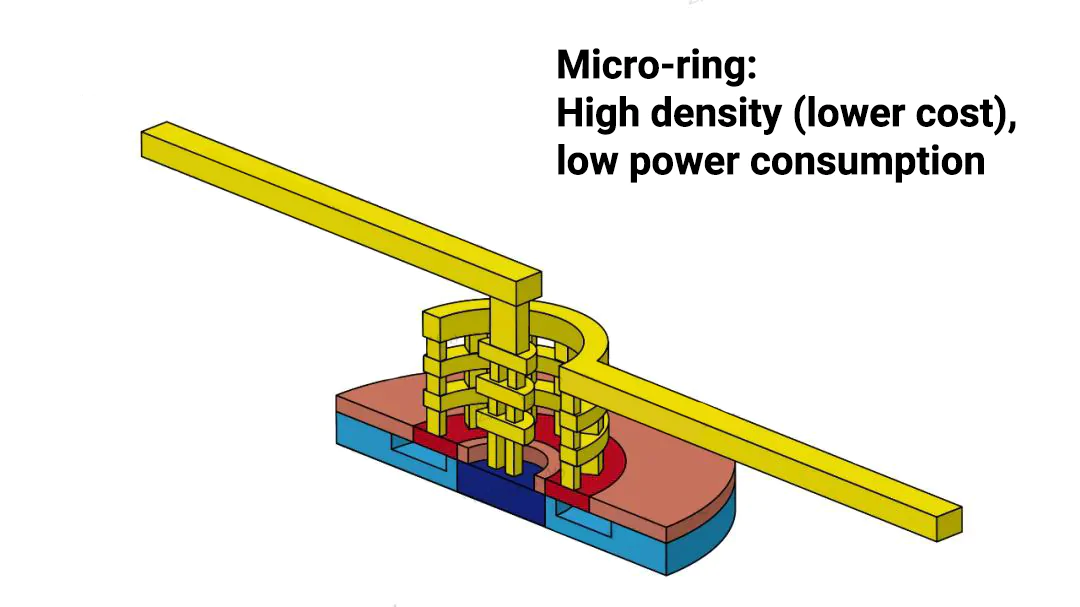

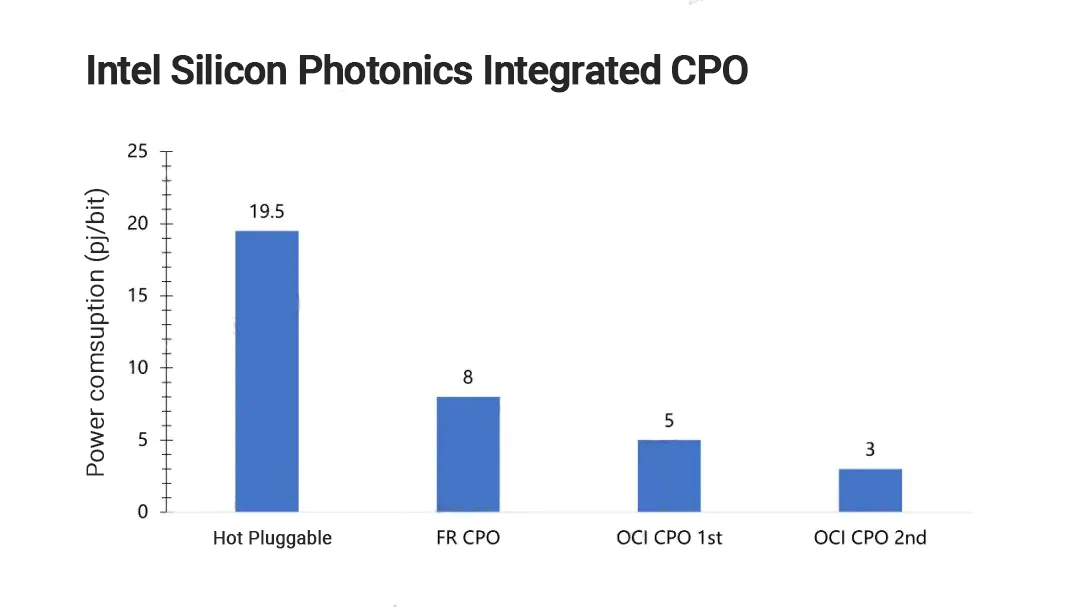

For instance, to meet the demanding power efficiency goals for AI silicon photonics modules, current 800G DR8 modules consume 13W, equating to 16 picojoules per bit (pj/bit). Reducing this to 1.5 pj/bit requires a 90% reduction in power consumption. Increasing bandwidth is one approach, but more significantly, CPO (Co-Packaged Optics) packaging can eliminate the need for DSPs, cutting power use in half without sacrificing RF performance, unlike LPO (Laser Package Optics). Replacing MZ modulators with micro-ring modulators can further reduce energy consumption.

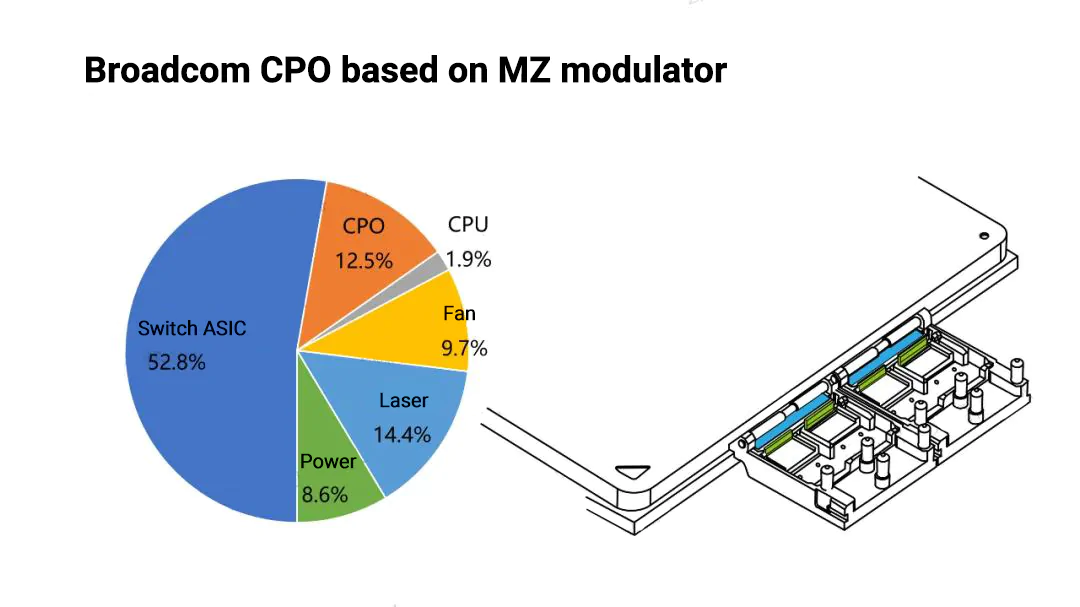

In 2022, Broadcom's analysis of power distribution in switches showed that lasers and CPO components (modulators, detectors, DRV, TIA) share power consumption evenly, with their CPO based on cascaded MZ modulators achieving 5.5 pj/bit.

Broadcom CPO based on MZ modulator

Broadcom CPO based on MZ modulator

MZ modulators have VπL of about 1-2 V.cm, while micro-ring modulators reduce this to 0.5 V.cm, enhancing efficiency with a smaller footprint.

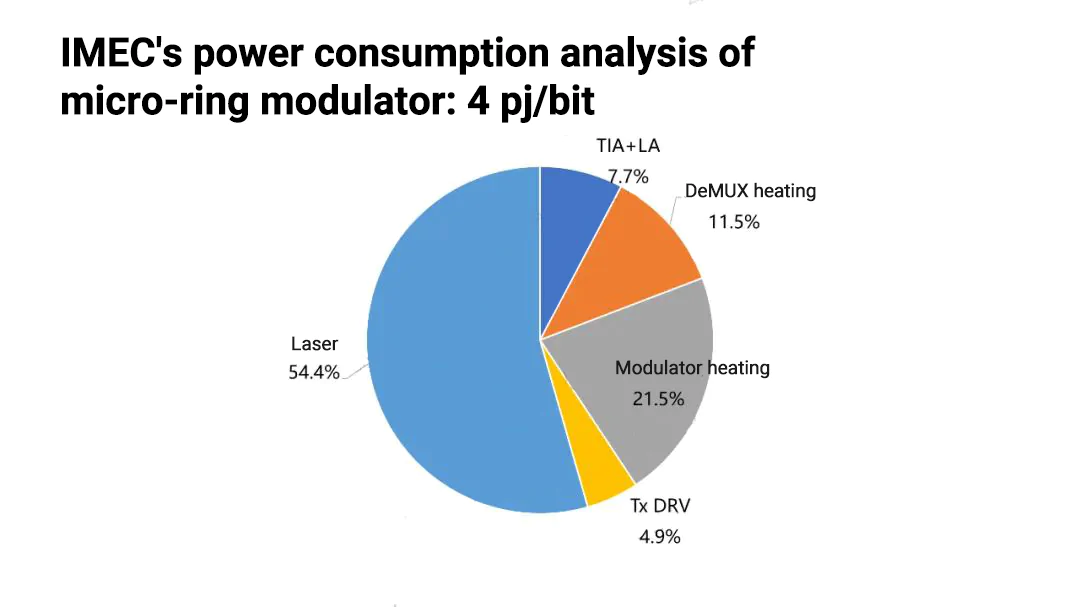

In 2023, IMEC conducted a detailed analysis of the power consumption for systems based on micro-ring modulators.

IMEC’s power consumption analysis of micro-ring modulator: 4pj/bit

IMEC’s power consumption analysis of micro-ring modulator: 4pj/bit

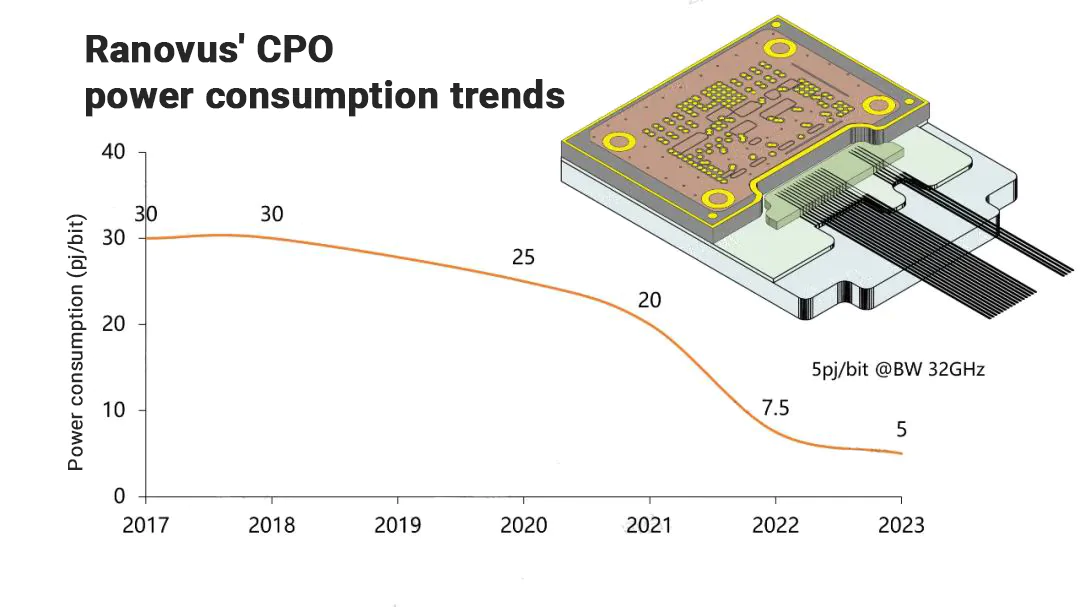

Ranovus uses micro-ring modulators.

Ranovus’ CPO power consumption trends

Ranovus’ CPO power consumption trends

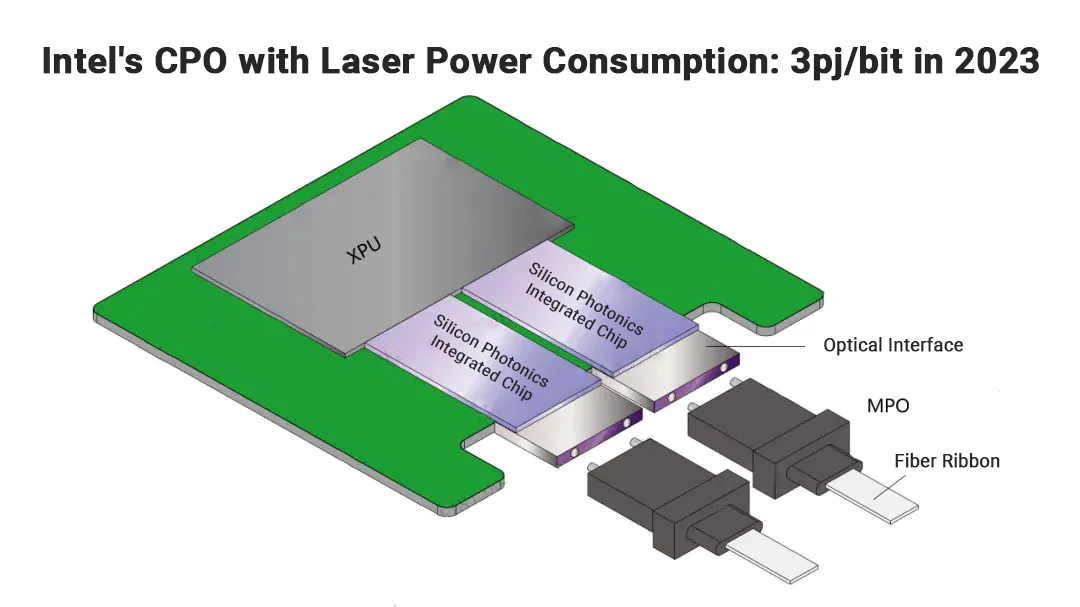

Intel also employs micro-ring modulators, and in 2023, Intel’s CPO with integrated lasers demonstrated power consumption of 3 pj/bit.

Intel silicon photonics integrated CPO

Intel silicon photonics integrated CPO

An analysis of CPO structures using micro-rings and MZ modulators shows that laser choice significantly impacts energy efficiency.

Below is the analysis of power consumption for CPO based on silicon photonics technology.

|

Research Unit |

CPO Composition |

Power Consumption per bit |

|

Broadcom (based on MZ Modulator) |

CPO includes laser |

11 pj/bit (estimated) |

|

CPO without laser |

5.5 pj/bit |

|

|

Intel (based on Micro-Ring Modulator) |

CPO includes laser |

3 pj/bit |

|

CPO without laser |

1.5 pj/bit (estimated) |

|

|

HP (based on Micro-Ring Modulator) |

CPO with (optical comb) multi-wavelength laser |

1.5 pj/bit |

Controlling laser selection and thermal compensation in micro-ring modulators can further reduce power consumption.

Below is the table of power consumption for micro-ring modulators from Ranovus, IMEC, Intel, and HP.

|

Research Unit |

Power Consumption per Bit |

Description |

Summary |

|

Ranovus |

5 pj/bit |

Includes laser and thermal compensation |

|

|

IMEC |

4 pj/bit |

Includes laser and thermal compensation |

|

|

Intel |

3 pj/bit |

Includes laser and thermal compensation |

|

|

HP |

1.5 pj/bit |

Includes laser, no thermal compensation |

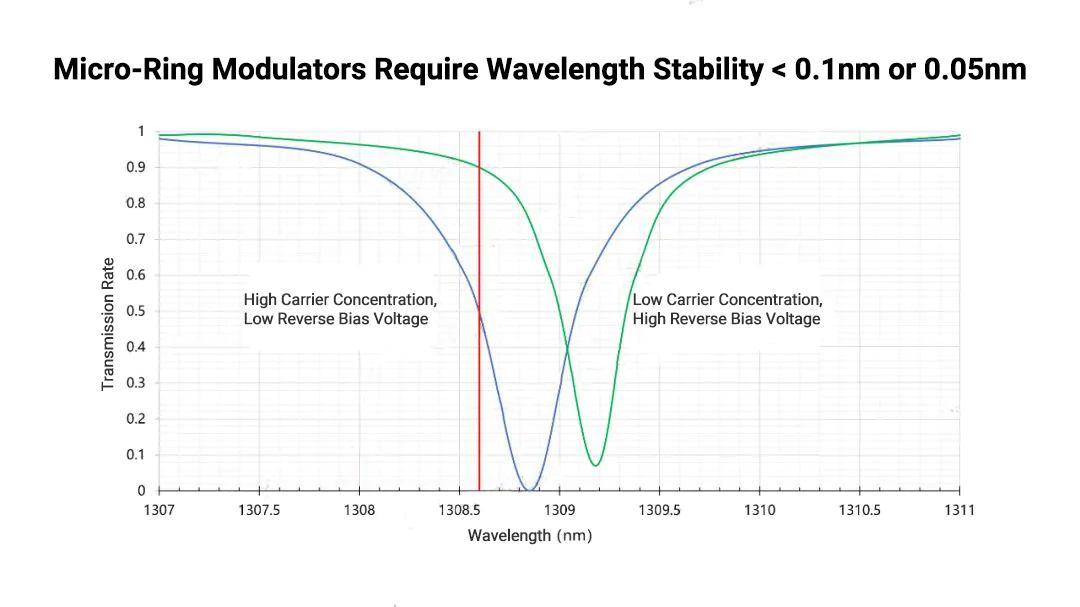

Why does Micro-ring need thermal compensation?

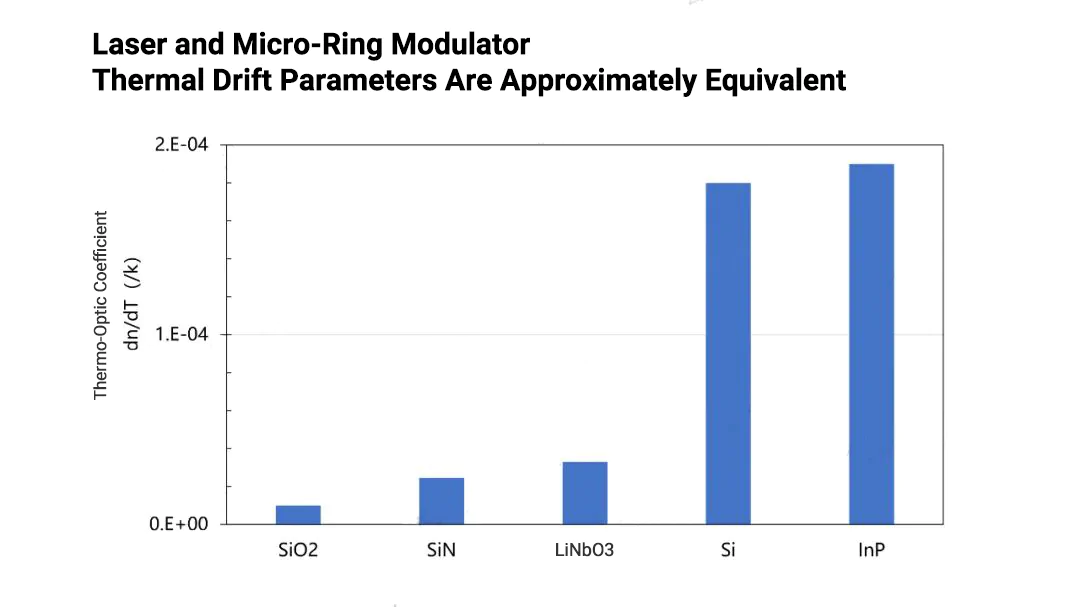

Micro-rings require thermal compensation due to resonance wavelength drift under varying bias voltages and temperatures, with drift coefficients around 0.03 nm/V for voltage and 0.1 nm/°C for temperature, necessitating precise wavelength stabilization when interfacing lasers with micro-ring modulators.

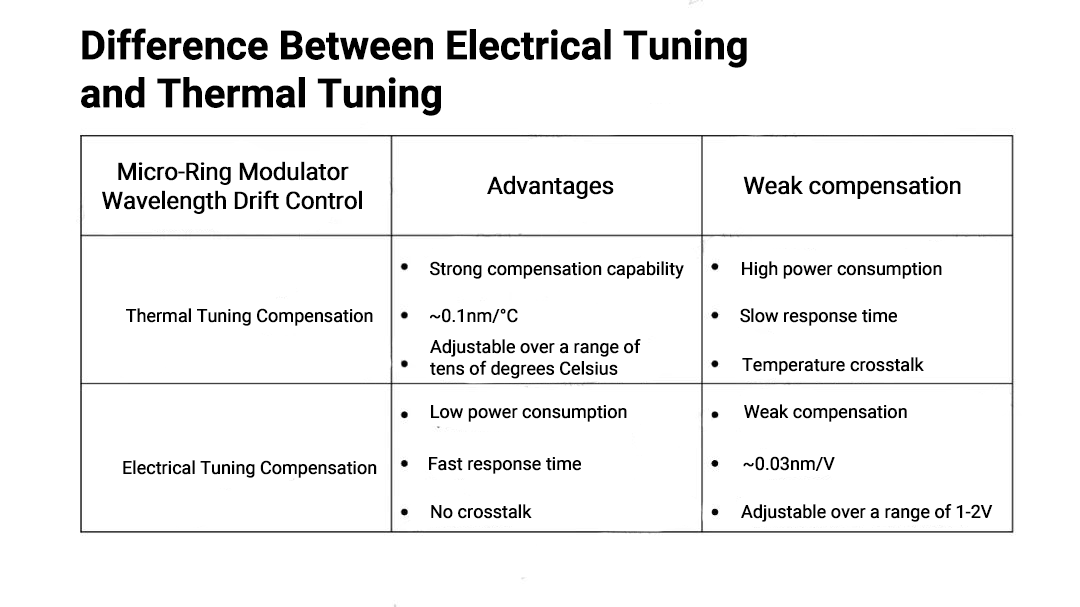

The wavelength stability of micro-ring modulators can be managed by either thermal tuning or electrical tuning. NVIDIA has specified a thermal tuning precision of 0.4°C. However, thermal tuning consumes significant power, while electrical tuning offers weaker performance. HP’s approach eliminates thermal tuning but uses PN heterojunctions of silicon and GaAs instead of pure silicon, which impacts reliability.

This results in trade-offs between performance, power consumption, and reliability in micro-ring designs.

Difference between electrical tuning and thermal tuning

Difference between electrical tuning and thermal tuning

Regarding thermal tuning, challenges include crosstalk and mutual thermal effects among cascaded micro-rings. To maximize wavelength alignment between micro-ring resonators and lasers, integrating lasers made of InP with silicon modulators is beneficial as their temperature drift coefficients are similar, reducing compensation difficulties.

However, integrating lasers also introduces reliability risks, as lasers are among the most failure-prone components in optical modules.

High Reliability

Regarding reliability, conventional optical modules generally require a laser FIT (Failure In Time rate) of 125, meaning a 5-year lifespan with a failure rate of 0.5%. Silicon photonics modules now target 100 FIT, with a 5-year failure rate of 0.4%, which appears acceptable. However, silicon photonics involve multiple integrated channels—like Broadcom's 6.4T CPO with 64 modulators and Intel's CPO with 96 micro-ring modulators per chip. Each modulator requires a laser, and with a laser FIT of 100, a 10-laser array could escalate the failure rate to 1000 FIT, or 4%.

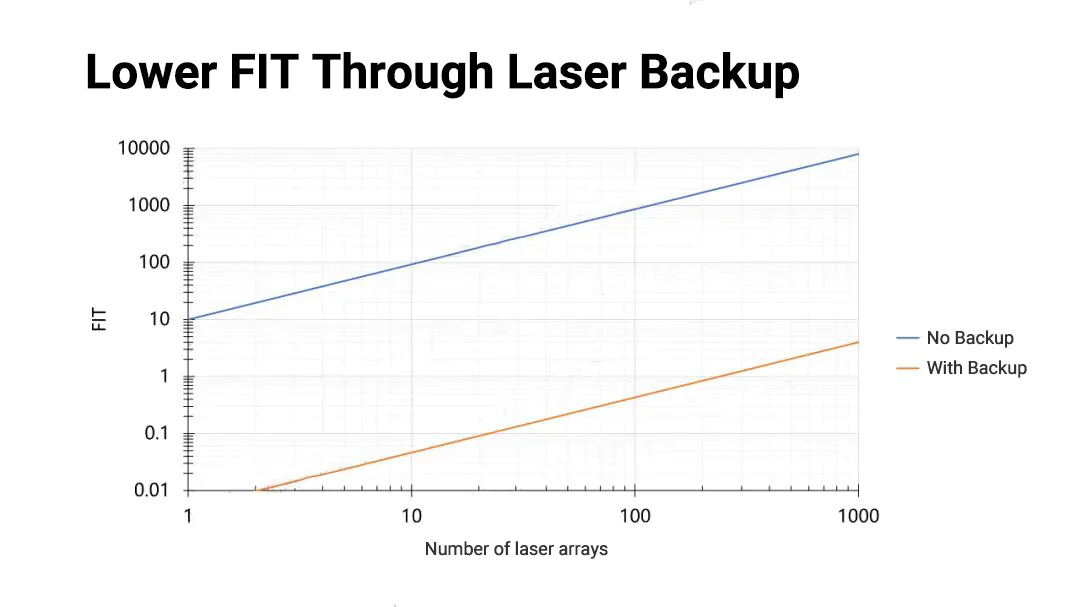

A key challenge is managing the FIT rate as it scales with laser array size. HP addresses this by using optical frequency combs with multi-wavelength lasers, where a single laser supports multiple micro-ring modulators, balancing low power consumption and high reliability. Intel initially paired one laser with each micro-ring modulator but began developing multi-wavelength lasers in 2023, reducing the number of lasers and thereby lowering the failure rate.

Another approach, similar to Finisar’s, involves adding backup lasers. Finisar developed a VCSEL-based multimode CPO for IBM, doubling the laser count and reducing the failure rate by three orders of magnitude. Intel also evaluated the reliability of backup lasers between 2020 and 2021, showing that backup lasers can significantly reduce failure rates.

Summary

Reducing energy consumption in optical modules involves multiple strategies. For standard 800G DR8 modules, typical energy usage is around 16 pj/bit. One approach is to eliminate the DSP, which can cut consumption to approximately 8 pj/bit, as demonstrated by Arista. Utilizing CPO packaging with external lasers in a one-to-many configuration can further reduce consumption to around 5 pj/bit, as seen in Broadcom's solution. Integrating micro-ring modulators can push this reduction to 3 pj/bit, a strategy employed by Intel. HP goes even further with micro-ring modulators and optical frequency comb lasers, achieving a remarkably low 1.5 pj/bit without thermal control.

To enhance reliability, strategies include using external lasers with ELSFP packaging, where one laser can drive multiple modulators, although additional MUX design is required. Integrated lasers combined with optical frequency combs and quantum dots can serve multiple micro-ring modulators without needing extra MUX units, thereby balancing efficiency. Another effective approach is incorporating backup lasers, which dramatically lower failure rates, as evidenced by various industry evaluations, including Intel's assessments between 2020-2021.

As NADDOD expands its portfolio to include silicon photonics module(1.6T/800G/400G), it continues to advance in the field of optical connectivity, offering innovative solutions that meet the growing demands of AI and high-speed data center applications.

800GBASE-2xSR4 OSFP PAM4 850nm 50m MMF Module

800GBASE-2xSR4 OSFP PAM4 850nm 50m MMF Module- 1NADDOD Launches 51.2T Ethernet Data Center Switches Powered by Broadcom Tomahawk 5

- 2Three Core Broadcom Optical Interconnect Technologies

- 3400G Coherent Optics: Breaking Through Bandwidth and Distance Barriers in DCI and MAN

- 4Vera Rubin Superchip - Transformative Force in Accelerated AI Compute

- 5NVIDIA GB300 Deep Dive: Performance Breakthroughs vs GB200, Liquid Cooling Innovations, and Copper Interconnect Advancements.